Page 19 of 22

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 4:46 pm

by BennVenn

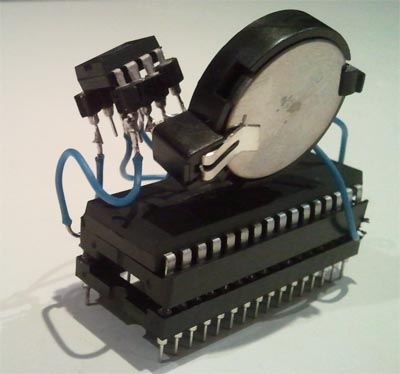

Too hot and now too stormy to work on the bug. So I made one of these...

Even included a sram battery management ic.

My FRAM ic has arrived. Just waiting on the sop to dip board for prototyping. I could dust off the cnc engraver and route my own board... see how the weather looks tomorrow.

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 5:56 pm

by HQ355

Aldi sell everything now lol

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 6:09 pm

by BennVenn

picked it up yesterday. I can't believe I've never had a bench vice for stuff like this!

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 6:41 pm

by Dylan

I've got one to. Used only for memcal soldering it's a ripper.

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 7:04 pm

by BennVenn

It was mentioned earlier in this thread that EPROM /CE is tied low permanently. This is not true. EPROM /OE is pulled low and /CE is switched via the CPU.

On the schematics, /CE and /OE are swapped. So going by the schematics yes /CE is held low via a 10k resistor and for an EPROM this won't make one bit of difference. The problem is when using any kind of RAM, holding /OE low and toggling /CE is acceptable though when a write is being commanded, all 3 control lines are low and this condition is illegal.

One of two things are going on. 1) the Dallas NVRAM IC has some kind of gating internal to prevent a latch-up condition, or 2) these pins are swapped on NVRAM boards.

Either way, my SRAM was being rapidly corrupted when inserted into an ECU and I believe this to be the problem. I suggest any future NVRAM designs address this issue (unless this is already addressed).

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 7:17 pm

by BennVenn

More problems! If we were to swap OE and CE so /CE is always tied low, /OE would be toggled by the CPU on a read request within a valid bus address (0x0000-0x7FFF) however when the CPU writes to the timer IC at a higher bus address it would corrupt data on the NVRAM as it's /CE is always tied low.

If we stick with the lines swapped, all is well except for the one condition were OE and RW are both low at the same time (when updating the NVRAM)

How does the original NVRAM board get around this without a NAND gate?

Edit: A15 to control EPROM /CE will solve all the problems!

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 7:49 pm

by Jayme

not sure if this helps.... you may as well be speaking chinese, I know next to nothing about how it actually works! but are you aware of the extra write wire we add to the unused pin at the end of the memcal socket?

- writewire.PNG (1.55 MiB) Viewed 7975 times

Re: FRAM NVRAM Board

Posted: Sat Mar 12, 2016 7:53 pm

by BennVenn

Im using rw from the edge connector. Interesting. Is that an 808?

Edit: yeah same pin. It runs up to edge connector pin 1. Wonder why it is chosen to solder to a via rather than a dedicated pad...

Re: FRAM NVRAM Board

Posted: Sun Mar 13, 2016 3:49 am

by antus

No reason. Both ways are valid.

Re: FRAM NVRAM Board

Posted: Sun Mar 13, 2016 8:22 am

by festy

I solder to the via because I think it's neater and gives a nice 'through hole' connection, and also leaves the card edge connector available (it's very convenient to be able to plug in a LA for diagnostics without having to solder or clip a stack of lines).

Not sure why you're having corruption issues, I've built heaps of BBSRAMs that have worked fine without any gating or line swapping.

What controller IC are you using? I'd assumed a ds1210 or bq2201 but from what I can see from the pic of your memcal, the wiring doesn't look right for either of those? Maybe I'm just confusing the red wire with the... other red wires

Here's a pic of the first BBSRAM I made about 5 years ago, no black magic required.

- diy-nvram.jpg (42.54 KiB) Viewed 7942 times